In any case, a Z80 version would require a new PCB design. The most time-critical path inside the FPGA is to the RAM and back: Since the RAM is organized in blocks which are distributed across the whole chip, some routes are really long. And routing delays within the CPU logic are probably not going to be the main timing bottleneck.

To implement the more complex instruction set of the Z80, there are certainly plenty of unused logic cells in the FPGA. So I think there is room for a streamlined Z80 implementation. For external bus cycles the FPGA would have to respect the exact host timing, but these are slow anyway.

#6502 emulator t code#

Thanks for the comments on a potential Z80 version, RÖB.įor fast code execution from internal RAM, being “cycle exact” should not matter at all - it’s invisible to the external host computer anyway, and decoupled from its clock.

Even then the Z80 also has a lot of indexed modes which would become a bottleneck and probably THE bottleneck that limits the overall achievable speed. However the Z80 (CISC) has many internal data paths and would require many extra gates. Well something like the RISC (like) 6502 doesn’t have a lot of different data paths so it’s easily sped up with some extra gates. Pushing the Z80 past 50MHz will require a lot of extra gates and a good clock domain scheme. The 6502 is very RISC like and the Z80 is definitely CISC.

If you abandon the Z80s peculiar clocking scheme (it was mostly done that way to refresh dynamic RAM) and aim for a cycle incorrect implementation then you would loos a lot of complexity and cost. The 6502 has a symmetric and linear clocking scheme. That’s not so easy to achieve with FPGA especially with something like the Z80 which has a very complex timing scheme. Posted in Misc Hacks Tagged 6502, 65c02, fpga Post navigation If you’ve got any cutting-edge 6502 hacks of your own (not a misprint!), let us know! We’ve seen the opposite before too, with a real 6502 paired with a FPGA acting as the rest of the computer. The pin-compatible design has been tested successfully in an Apple II and a Commodore 8032, as well as a variety of vintage chess computers. It allows the chip to accelerate plenty of tasks without completely flipping out when used with older hardware that can’t run at anywhere near 100MHz.

#6502 emulator t full#

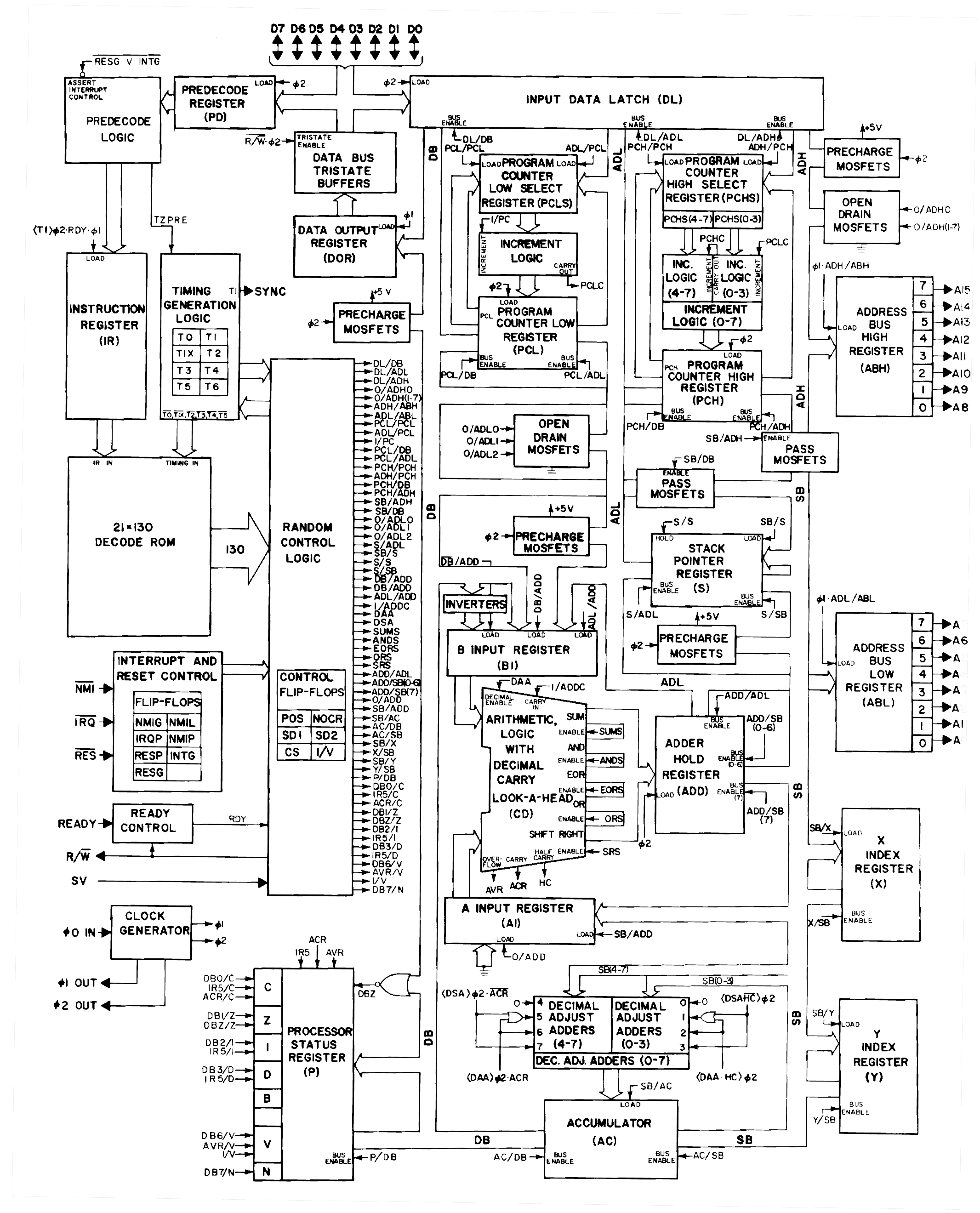

The CPU then runs at full 100MHz speed except when it needs to talk to those I/O addresses. It copies RAM and ROM from the host machine into its own internal 64 kilobyte RAM, minus the areas used for memory-mapped I/O by the host. However, internally, the CPU core runs at 100MHz. The FPGA is set up to access the external CPU bus with the timing matched to the clock of the host machine. then packaged that core in a Spartan-6 FPGA and placed it on a small PCB the size of the original 65C02’s 40-pin dual inline package. The CPU core was borrowed from work by and extended with 65C02 functionality by and. A popular variant is the 65C02, and decided to whip up a pin-compatible FPGA version that runs at a blazing 100MHz. In various modified versions, it powered everything from the Commodore 64 to the Nintendo Entertainment System, and showed up in a million other applications too. The MOS Technology 6502 CPU was a popular part in its day.

0 kommentar(er)

0 kommentar(er)